728x90

20.2

Show the micro-operations and control signals in the same fashion as Table 20.1 for the processor in figure 20.5 for the following instructions:

- Load Accumulator

t1: MAR <- (IR(address)) C8

t2: MBR <- Memory C5, CR

t3: AC <- (MBR) C10 - Store Accumulator

t1: MAR <- (IR(address)) C8

t2: MBR <- AC C11

t3: memory <- MBR C12,Cw - Add to Accumulator

t1: MAR <- (IR(address)) C8

t2: MBR <- Memory C5, CR

t3: AC <- AC + MBR C6, C7, C9, Call - AND to Accumulator

t1: MAR <-(IR(address)) C8

t2: MBR <- Memory C5, CR

t3: AC <- (AC) AND (MBR) Call, C6, C7, C9 - Jump

t1: PC <- IR(address) C3 - Jump if AC = 0

Test AC and active C3 if AC = 0 - Complement Accumulator

t1: AC <- (A̅C̅) CAll,C6,C7,C9

20.3

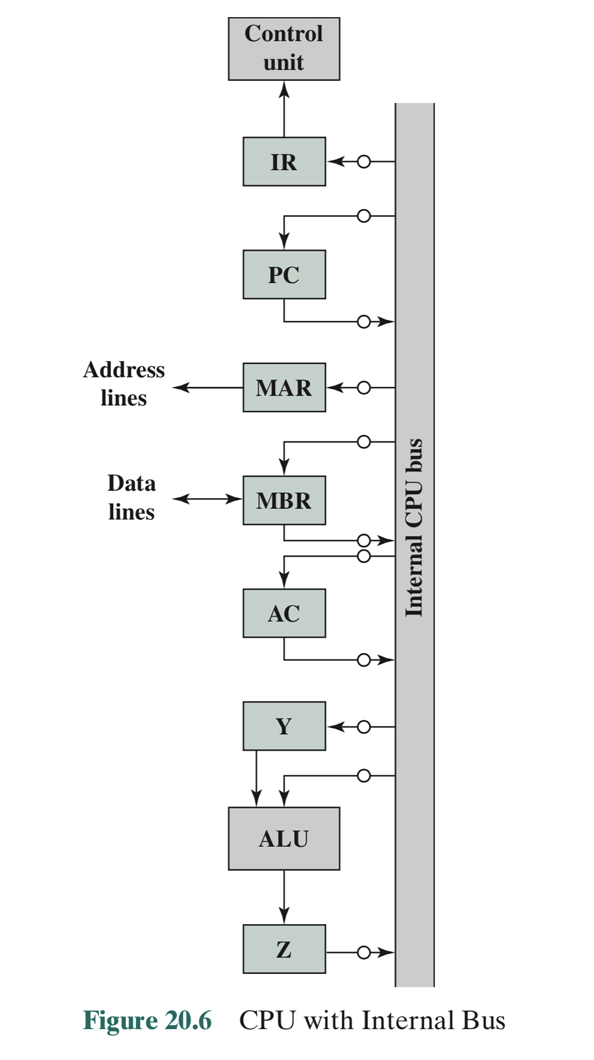

Assume that propagation delay along the bus and through the ALU of Figure 20.6 are 20 and 100ns, respectively. The time required for a register to copy data from the bus in 10ns. What is the time that must be allowed for

- data from one register to another?

propagation time of bus + copy time = 20ns + 10ns = 30ns - the program counter

Z <- PC+1 : propagation time of bus + propagation time for ALU + copy time = 20ns + 10ns + 100ns = 130ns

PC <- Z : propagation time of bus + copy time = 30ns

total 160ns

20.4

Write the sequence of micro-operations required for the bus structure of Figure 20.6 to add a number to the AC when the number is

- immediate operand

t1: Y <- (IR(address))

t2: Z <- (AC) + (Y)

t3: AC <- (Z) - direct-address operand

t1: MAR <- (IR(address))

t2: MBR <- (Memory)

t3: Y <- (MBR)

t4: Z <- (AC) + (Y)

t5: AC <- (Z) - indirect-address operand

t1: MAR <- (IR(address))

t2: MBR <- (Memory)

t3: MAR <- (MBR)

t4: MBR <- Memory

t5: Y <- (MBR)

t6: Z <- (AC) + (Y)

t7: AC <- (Z)

728x90

'Computer Science > Computer Architecture & Organization' 카테고리의 다른 글

| Booth Algorithm (0) | 2020.06.23 |

|---|---|

| 컴퓨터 구조 용어 정리 (0) | 2020.06.22 |

| CA & CO Chapter 10 practice problem (0) | 2020.05.23 |

| CA & CO Chapter 2 성능문제 (0) | 2020.05.02 |

| CA & CO Chapter 5 practice problem (0) | 2020.04.26 |

댓글